Pre-Summer Special Limited Time 70% Discount Offer - Ends in 0d 00h 00m 00s - Coupon code = getmirror

Pass the ARM AAE EN0-001 Questions and answers with ExamsMirror

Exam EN0-001 Premium Access

View all detail and faqs for the EN0-001 exam

727 Students Passed

96% Average Score

97% Same Questions

How many ARM core registers and PSRs (Program Status Registers) are available to the programmer in User mode on a Cortex-A9?

Which of the following options lists the power modes in order of increasing overhead of entry and exit from run mode?

What is the value of r0 after executing the following instruction sequence?

MOV r0, #200

MOV r5, #1

STR r3, [r0, r5, LSL#3]!

In a symmetric multi-processing (SMP) software architecture, which of the following pairs of statements are TRUE? (Select the option in which BOTH statements are TRUE).

What debugger view can you use to determine which function caused an exception?

Assume a Big-Endian (BE) memory system with the following memory contents.

Byte Address Contents

0x100 0x11

0x101 0x22

0x102 0x33

0x103 0x44

If R5 = 0x100, what are the contents of R4 after performing the following operation?

LDR R4, [R5]

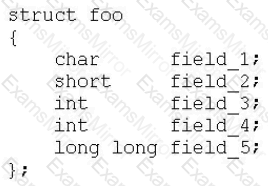

According to the EABI. what would the C size of () operator return when given the following structure?

The following C function is compiled with hard floating point linkage.

float function(int a, float b, int c, float d);

Which register is used to pass argument c?

In the Generic Interrupt Controller (GIC) architecture, which of the following ID numbers are reserved for interrupts that are private to a CPU interface?

When should an ISB instruction be used?

TOP CODES

Top selling exam codes in the certification world, popular, in demand and updated to help you pass on the first try.