Pre-Summer Special Limited Time 70% Discount Offer - Ends in 0d 00h 00m 00s - Coupon code = getmirror

Pass the ARM AAE EN0-001 Questions and answers with ExamsMirror

Exam EN0-001 Premium Access

View all detail and faqs for the EN0-001 exam

727 Students Passed

96% Average Score

97% Same Questions

Is it possible to use an interrupt controller based on the Generic Interrupt Controller (GIC) architecture in a device built around a single core Cortex-A9 MPCore processor?

A deeply embedded real-time industrial control system is missing some hard real-time interrupt deadlines. Which of the following performance analysis techniques is the most suitable for identifying which routines are causing the problem?

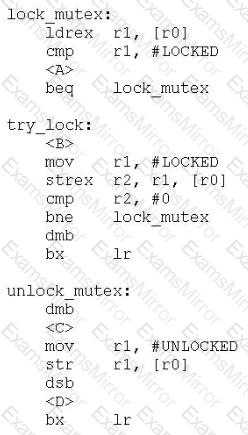

The following pair of functions implement a simple mutex spinlock which might be used to protect a critical code section in a multi-threaded application. The address of the lock variable is in r0.

In order to minimize power while waiting for the lock to be available. SEV and WFE instructions can be used to place the processor in a low power state while waiting for the lock to become available. At which points should these instructions be placed?

A simple system comprises of the following memory map:

Flash - 0x0 to 0x7FFF

RAM - 0x10000 to 0X17FFF

When conforming to the ABI, which of the following is a suitable initial value for the stack pointer?

Which of the following properties is a required characteristic of a Symmetric Multiprocessing (SMP) system?

Using a lower optimization level when compiling will:

An advantage of removable flash memory over built-in flash memory is that:

On an ARM processor that does not implement Security Extensions, which one of the following can be the starting address of the exception vector table?

Which of the following operations would count as intrusive to normal processor operation?

In a Cortex-A9 processor, when the Memory Management Unit (MMU) is disabled, which of the following statements is TRUE? (VA is the virtual address and PA is the physical address)

TOP CODES

Top selling exam codes in the certification world, popular, in demand and updated to help you pass on the first try.